Register-transfer level (RTL) is a level of design abstraction meant to make it easier to model circuits in a way that is easier to understand but also allows for the necessary low-level representations and the actual, physical wiring needed to be derived from that design as well. It is used in hardware description languages like Verilog and VHDL which describe hardware and is an important step in almost any digital design today. The name RTL is derived from the fact that the this level of language emphases the description of the transfer of signals between registers instead of the individual logic gates at transistor-level.

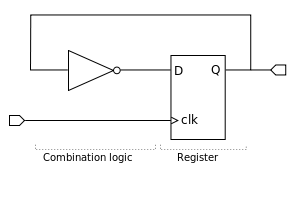

To use an example from Wikipedia, the following toggle circuit diagram created by user AndyHe829:

when written in VHDL at RTL, would look as follows:

D <= not Q;

process(clk)

begin

if rising_edge(clk) then

Q <= D;

end if;

end process;

The idea behind RTL designs is to use the flow of digital signals between logical operations and the hardware registers that receive them, and use those terms to model a synchronous digital circuit. Synchronous circuits always have 2 types of components:

- combinational logic

These components are usually logic gates, and they perform all the logical operations of the circuit. These are described in an RTL language using more familiar constructs such as the if-then-else statements of regular programming languages, and other common arithmetic operations.

- registers

These synchronize the operation of the circuit to the edges of the clock signals. Registers are the only components with memory properties in a synchronous digital circuit. The designer will declare the register they plan to use in the first step of creating their design in RTL.

Without RTL languages and designs, figuring out how to plan and implement the circuits necessary for everyday computation would be massively more complicated and difficult for engineers to achieve.

© BrainMass Inc. brainmass.com May 1, 2024, 11:06 pm ad1c9bdddf